- Quadcept Support

- 15/05/01 11:59:47

お問い合わせいただきありがとうございます。

BGAのパッド間に動的ベタを配置する方法についてですが、

今回の場合、DRC/MRC設定で[ベタ]と[SMD]のクリアランスの値と

ベタの[外形線幅]と[塗りつぶし線幅]の値を変更することで

パッド間への動的ベタの配置が可能になります。

具体的な手順としましては、

まず、DRC/MRC設定画面を開いていただき(【各種設定】→【DRC/MRC設定】)、

[クリアランス]の[詳細設定]タブにございます

[ベタ]と[SMD]の交わるボックスの値を0.1mmにご設定くださいませ。

※astro_pll_mb1500様は既にベタとパッドのクリアランスを

0.1mmにご設定いただいているとのことですが、

念のため、ご確認いただけますと幸いです。

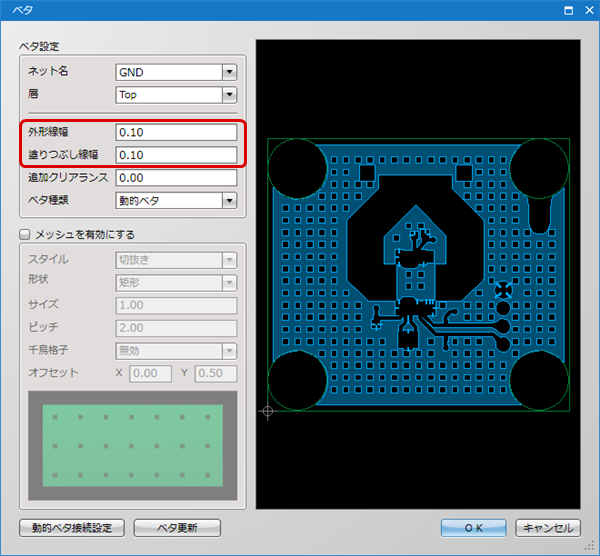

次に、配置した動的ベタをダブルクリックしていただき、

表示されます[ベタ]ウィンドウで[外形線幅]と[塗りつぶし線幅]の値を

それぞれ0.1mmにご設定ください。

この設定により動的ベタ配置時のベタ作成の線幅が0.1mmとなり、

BGAの端子間にベタを配置することが可能になるかと思います。

その後、[ベタ]ウィンドウで[ベタ更新]をクリックし、

ベタ更新していただくことで、

パッド間に動的ベタが配置されるかと思います。

以上、お手数ですが一度お試しくださいませ。