- Quadcept Support

- 13/10/21 14:48:00

お問い合わせいただきありがとうございます。

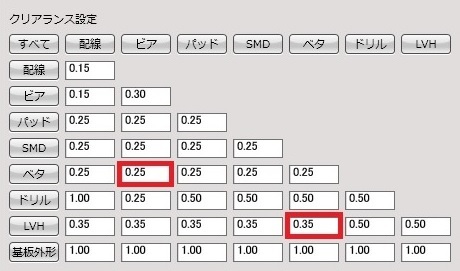

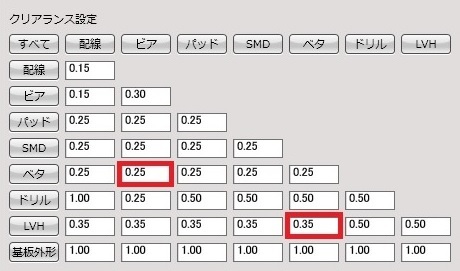

動的ベタとビアとのクリアランス設定についてですが、対象のビアの状態によって

「ベタ-LVH」か「ベタ-ビア」か、どちらの項目の設定かが異なってまいります。

※LVH(Landless Via Hole)とは、内層で接続のために設けられたランド(銅箔)がないビアに対するクリアランス値を設定します。

クリアランス設定の内容についてはオンラインマニュアルにも記載がございますので、

こちらお時間ある時にでもご参照いただけますと幸いです。

■クリアランス設定について

http://4cept.com/ja/manual/pcb/post-6

今回の場合、hide様の対象とされているビアがどちらの状態であるのか、

いただきましたキャプチャからでは判断が難しいのですが、「ベタ-ビア」の設定も

一度お試しいただけますと幸いです。

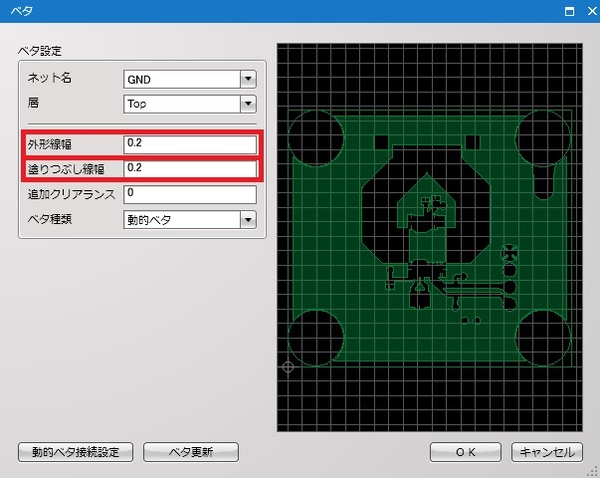

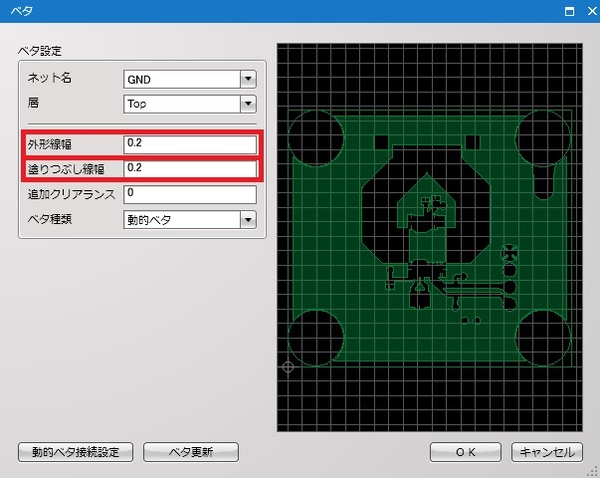

また、計算上はスリットが作成(クリアランス同士が繋がっている状態)にならないクリアランス設定であるにもかかわらず

スリットが作成されている場合、クリアランス同士の間の距離より、ベタの「外形線幅」「塗りつぶし線幅」が大きく

ベタがクリアランス同士の間に入っていくことができず、繋がっていることが考えられます。

対象のベタをダブルクリック(もしくは選択状態でのプロパティウィンドウ)にて表示されます

「外形線幅」「塗りつぶし線幅」を小さい値へと変更してみてくださいませ。

お手数をおかけして恐縮ですが、こちらも一度お試しいただけますと幸いです。

以上どうぞよろしくお願いいたします。

動的ベタとビアとのクリアランス設定についてですが、対象のビアの状態によって

「ベタ-LVH」か「ベタ-ビア」か、どちらの項目の設定かが異なってまいります。

※LVH(Landless Via Hole)とは、内層で接続のために設けられたランド(銅箔)がないビアに対するクリアランス値を設定します。

クリアランス設定の内容についてはオンラインマニュアルにも記載がございますので、

こちらお時間ある時にでもご参照いただけますと幸いです。

■クリアランス設定について

http://4cept.com/ja/manual/pcb/post-6

今回の場合、hide様の対象とされているビアがどちらの状態であるのか、

いただきましたキャプチャからでは判断が難しいのですが、「ベタ-ビア」の設定も

一度お試しいただけますと幸いです。

また、計算上はスリットが作成(クリアランス同士が繋がっている状態)にならないクリアランス設定であるにもかかわらず

スリットが作成されている場合、クリアランス同士の間の距離より、ベタの「外形線幅」「塗りつぶし線幅」が大きく

ベタがクリアランス同士の間に入っていくことができず、繋がっていることが考えられます。

対象のベタをダブルクリック(もしくは選択状態でのプロパティウィンドウ)にて表示されます

「外形線幅」「塗りつぶし線幅」を小さい値へと変更してみてくださいませ。

お手数をおかけして恐縮ですが、こちらも一度お試しいただけますと幸いです。

以上どうぞよろしくお願いいたします。

- hide

- 13/10/21 15:04:51

ご回答ありがとうございます。

今回の例では、対称のビアはベタ-LVH間のクリアランス設定が適用されている事を確認しました。

また、ご指摘頂いた通り「外形線幅」や「塗りつぶし線幅」の値を小さくする事で、クリアランス間のスリットが無くなる事も確認できました。

追加で1点疑問なのですが、自身の環境では「外形線幅」や「塗りつぶし線幅」を0.1未満の値にしても反映されず0.1になってしまいます。

「外形線幅」や「塗りつぶし線幅」は0.1未満の値にする事はできないのでしょうか?

今回の例では、対称のビアはベタ-LVH間のクリアランス設定が適用されている事を確認しました。

また、ご指摘頂いた通り「外形線幅」や「塗りつぶし線幅」の値を小さくする事で、クリアランス間のスリットが無くなる事も確認できました。

追加で1点疑問なのですが、自身の環境では「外形線幅」や「塗りつぶし線幅」を0.1未満の値にしても反映されず0.1になってしまいます。

「外形線幅」や「塗りつぶし線幅」は0.1未満の値にする事はできないのでしょうか?

- Quadcept Support

- 13/10/21 17:22:41

ご連絡いただきありがとうございます。

クリアランス設定と外形・塗りつぶし線幅の設定について、ご確認いただきありがとうございます。

また、hide様のご指摘の通り、ベタの「外形線幅」「塗りつぶし線幅」は共に

最小設定値を「0.1」に規定させていただいております。

これは製造データにおいて「外形線幅」「塗りつぶし線幅」が「0」では製造ができないため

最小値を規定しておく必要があり、実際の基板製造の精度なども含めまして、弊社の設計者とも協議し

「0.1」とさせていただいております。

現状では「0.1」と規定させて頂いておりますが

今後、開発をしていく中で変更していくことはもちろん可能でございます。

「0.1」以下の数値設定は必要となってまいりますでしょうか?

ご意見聞かせて頂けますと幸いです。

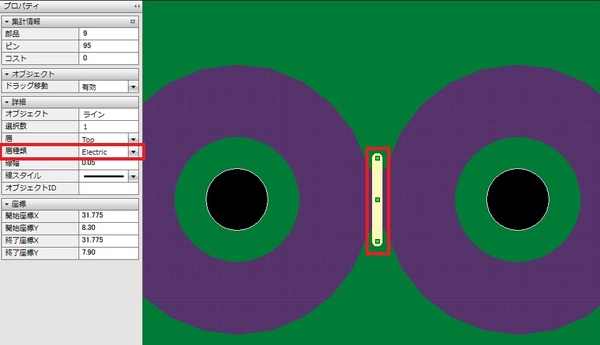

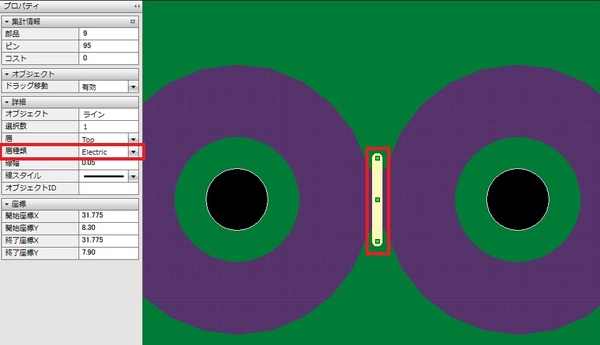

現状での回避策としては、「ライン」や「矩形」などのオブジェクトを

線幅0.1以下としていただき、それを任意の場所に【層種類:Electric】として

配置していただくことで、データ上は銅箔として扱うことができます。

スリットをどうしても分断するといこうとでしたら

回避策となりますが、お試しいただけますと幸いです。

以上どうぞよろしくお願いいたします。

クリアランス設定と外形・塗りつぶし線幅の設定について、ご確認いただきありがとうございます。

また、hide様のご指摘の通り、ベタの「外形線幅」「塗りつぶし線幅」は共に

最小設定値を「0.1」に規定させていただいております。

これは製造データにおいて「外形線幅」「塗りつぶし線幅」が「0」では製造ができないため

最小値を規定しておく必要があり、実際の基板製造の精度なども含めまして、弊社の設計者とも協議し

「0.1」とさせていただいております。

現状では「0.1」と規定させて頂いておりますが

今後、開発をしていく中で変更していくことはもちろん可能でございます。

「0.1」以下の数値設定は必要となってまいりますでしょうか?

ご意見聞かせて頂けますと幸いです。

現状での回避策としては、「ライン」や「矩形」などのオブジェクトを

線幅0.1以下としていただき、それを任意の場所に【層種類:Electric】として

配置していただくことで、データ上は銅箔として扱うことができます。

スリットをどうしても分断するといこうとでしたら

回避策となりますが、お試しいただけますと幸いです。

以上どうぞよろしくお願いいたします。

- hide

- 13/10/28 15:45:55

ご回答ありがとうございます。

現状ではベタの「外形線幅」「塗りつぶし線幅」は共に

最小設定値を「0.1」に規定されているという事で納得できました。

「0.1mm」以下の数値設定についてですが、個人的には対応して頂けるとありがたいです。

通常のサブトラクティブ基板では必要ないかもしれませんが、LSIパッケージなどに利用されるビルドアップ基板などで

残存ベタの幅が0.1mm以下になる場合などもあるのではないかと考えております。

また、作成した基板データをシミュレーションに利用する事などがあるので、ある程度非現実な値にも対応して頂けると非常にモデルが作成しやすいと思います。

よって、優先度としては低くても問題ありませんので、今後対応頂けると非常にありがたいです。

ご検討を頂ければ幸いです。

現状ではベタの「外形線幅」「塗りつぶし線幅」は共に

最小設定値を「0.1」に規定されているという事で納得できました。

「0.1mm」以下の数値設定についてですが、個人的には対応して頂けるとありがたいです。

通常のサブトラクティブ基板では必要ないかもしれませんが、LSIパッケージなどに利用されるビルドアップ基板などで

残存ベタの幅が0.1mm以下になる場合などもあるのではないかと考えております。

また、作成した基板データをシミュレーションに利用する事などがあるので、ある程度非現実な値にも対応して頂けると非常にモデルが作成しやすいと思います。

よって、優先度としては低くても問題ありませんので、今後対応頂けると非常にありがたいです。

ご検討を頂ければ幸いです。

- Quadcept Support

- 13/10/28 16:35:04

ご要望いただきありがとうございます。

優先度は低いけれども、ビルドアップ基板やシミュレーションなど

活用する機会はありそうということですね。

開発、設計者とも協議しまして、対応を検討してまいりたいと思います。

貴重なご意見をありがとうございます!

優先度は低いけれども、ビルドアップ基板やシミュレーションなど

活用する機会はありそうということですね。

開発、設計者とも協議しまして、対応を検討してまいりたいと思います。

貴重なご意見をありがとうございます!