- Quadcept Support

- 14/12/05 14:40:33

まず、ネットクラスでGNDを分けて同ネットクリアランスの設定を行う必要があります。

1:ネットクラスの振り分け

2:同ネットクリアランス設定

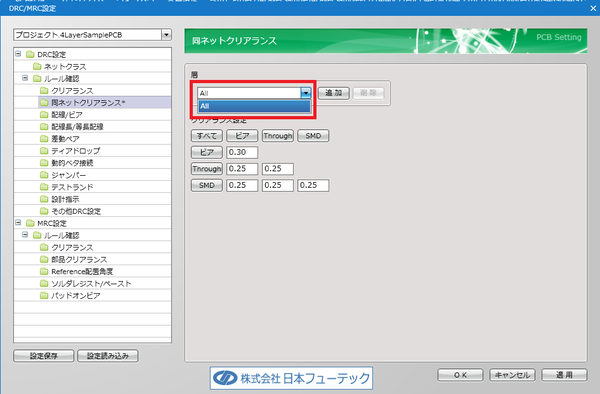

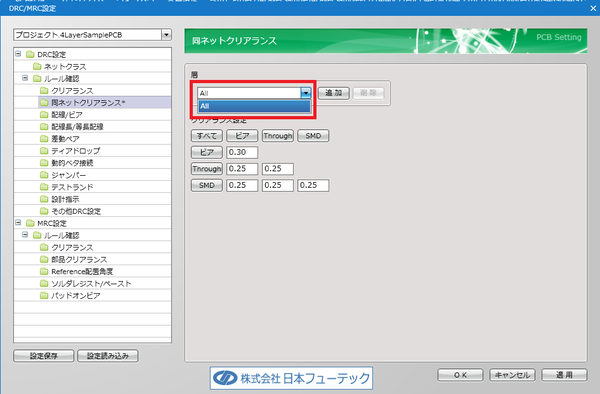

上部メニュー【各種設定】→【DRC/MRC設定】で【同ネットクリアランス】を選択します。

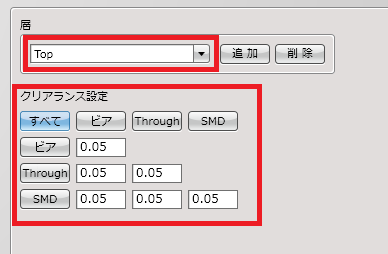

同ネットクリアランスはデフォルトで下記のようになっております。

この「All」というのは、全層に対する同電位クリアランスが行われているという意味です。

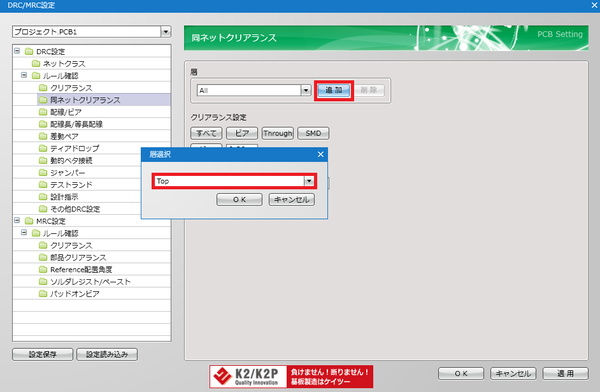

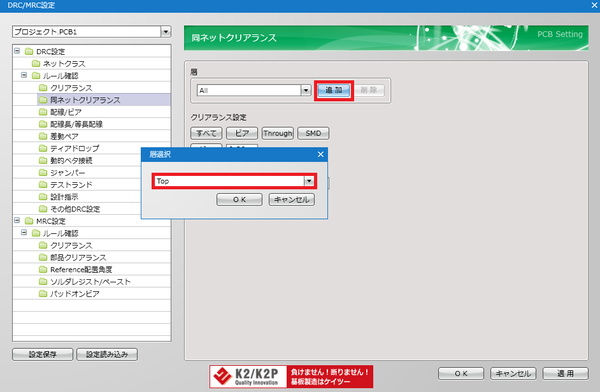

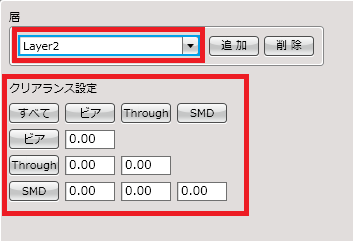

TOPと2層目の最小gapを0.05にする場合は、

下記のように層を追加し、個別で設定できるようにします。

上記の場合、topが追加され、topだけの同電位クリアランスが設定できます。

このように、topと2層目を個別で0.05mmで設定すると、

同電位クリアランスをDRCでチェックすることが可能です。

以上、ご確認の程、よろしくお願いいたします。

- kkanehisa2000

- 14/12/05 15:29:00

回答ありがとうございます。

しかし、この設定だと、

L1-L2間VIAとL1-L2間VIAのGAPのみを0.05としたいのですが、

L1-L2間VIAとL2-L3間VIAのGAPも0.05となってしまう。=>これは0としたい。

このような設定は可能でしょうか?

- Quadcept Support

- 14/12/05 16:32:01

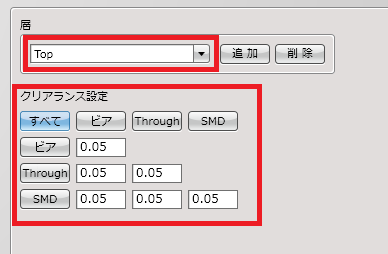

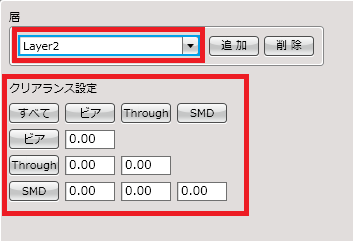

L1-L2間VIA同士は、TOPを0.05にすることでエラー検出し、

L1-L2とL2-L3はLayer2の設定を0にすることでいかがでしょうか?

- kkanehisa2000

- 14/12/05 17:36:56

>L1-L2間VIA同士は、TOPを0.05にすることでエラー検出し、

>L1-L2とL2-L3はLayer2の設定を0にする

L2-L3間via同士はLayer3の設定を0.05にすると

L2-L3とL3-L4はLayer3の設定はできなくなってしまいます。。。

3層以上の場合はどうすればよいですか?

- Quadcept Support

- 14/12/05 18:11:35

イメージを正しく共有させてもらいたいのですが、

例えば4層基板の場合、下記ということで間違いないでしょうか?

・L1では、L1-L2間のVia同士を0.05に設定

・L2では、L1-L2とL2-L3のViaを0、L2-L3間のVia同士を0.05

・L3では、L2-L3とL3-L4のViaを0、L3-L4間のVia同士を0.05

・L4では、L3-L4間のVia同士を0.05

上記の場合、現状の仕様では、自動でのチェックは厳しいです。。

すべての層を0.05に設定していただき、DRCエラーが多数検出されますので、

そちらを「承認済み」として運用回避する方法となります。

イメージが間違っていたら申し訳ございません。

ご意見いただければ幸いです。